### **LP3936**

# Lighting Management System for Six White LEDs and One RGB or FLASH LED

### **General Description**

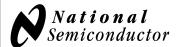

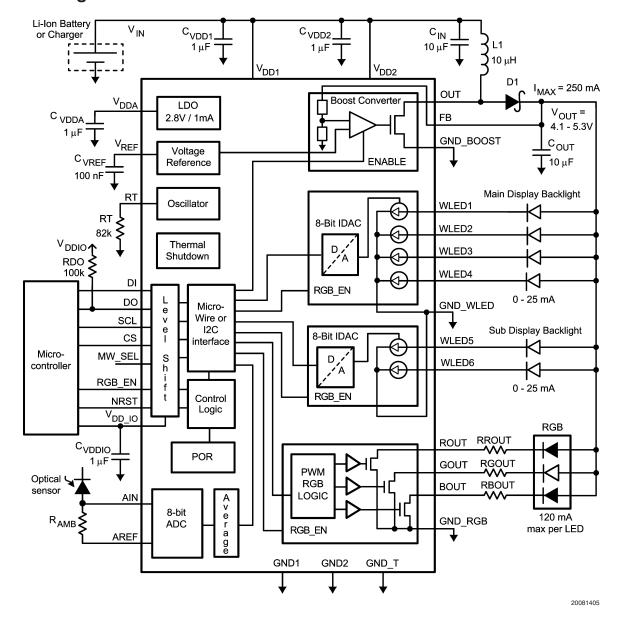

LP3936 is a complete lighting management system designed for portable wireless applications. It contains a boost DC/DC converter, 4 white LED drivers to drive the main LCD panel backlight, 2 white LED drivers for sub-LCD panel and 1 set of RGB LED drivers.

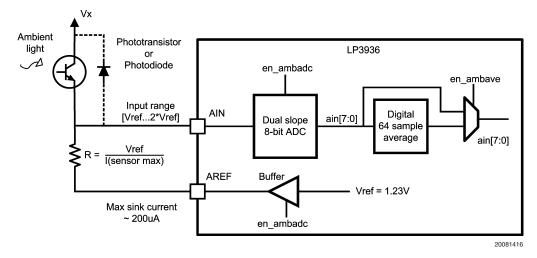

Both WLED groups have 8-bit programmable constant current drivers that are separately adjustable and matched to 1% (typ.). For efficient backlighting the backlight intensity can be adjusted using the 8-bit ADC with ambient light detection circuit.

The RGB LED drivers are PWM-driven with programmable color, intensity and blinking patterns. In addition, they feature a FLASH function to support picture taking with camera-enabled cellular phones.

An efficient magnetic boost converter provides the required bias operating from a single Li-Ion battery. The DC/DC converter output voltage is user programmable for adapting to different LED types and for efficiency optimization. All functions are software controllable through an I<sup>2</sup>C and MicroWire/SPI compatible interface and 16 internal registers

#### **Features**

- High Efficiency 250 mA Magnetic Boost DC-DC Converter with Programmable Output Voltage

- PWM controlled RGB LED drivers with programmable color, brightness, turn on/off slopes and blinking

- FLASH function with 3 drivers, each up to 120 mA current

- 4 constant current White LED drivers with programmable 8-bit adjustment (0 ... 25 mA/LED)

- 2 constant current White LED drivers with programmable 8-bit adjustment (0 ... 25 mA/LED)

- 8-bit ADC for ambient light sensor with averaging

- Combined MicroWire/SPI and I<sup>2</sup>C compatible serial interface

- Low current Standby mode (software controlled)

- Low voltage digital interface down to 1.8V

- Space efficient 32-pin thin CSP laminate package

### **Applications**

- Cellular Phones

- PDAs

### **Typical Application**

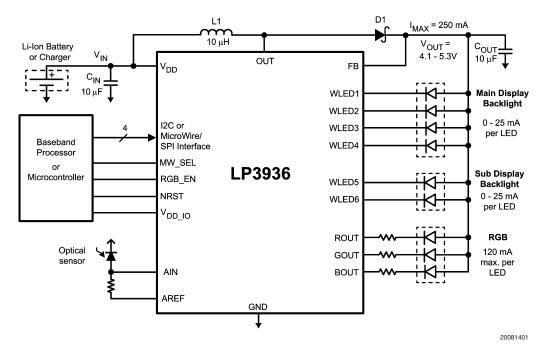

### **Connection Diagrams and Package Mark Information**

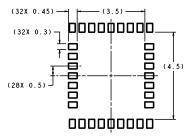

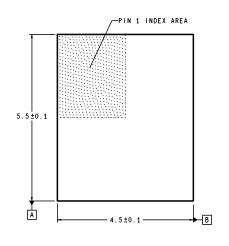

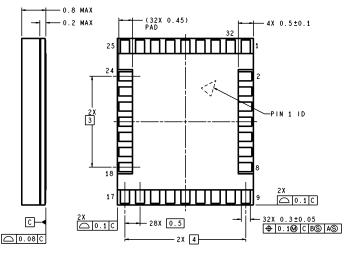

32-Lead Thin CSP Package, 4.5 x 5.5 x 0.8 mm, 0.5 mm pitch See NS Package Number SLD32A

20081404

Note: The actual physical placement of the package marking will vary from part to part. The package marking "XY" designates the date code. "UZ" and "TT" are NSC internal codes for die manufacturing and assembly traceability. Both will vary considerably.

Package Mark—Top View

### **Ordering Information**

| Order Number | Package Marking | Supplied As               |

|--------------|-----------------|---------------------------|

| LP3936SL     | LP3936SL        | 1000 units, Tape-and-Reel |

| LP3936SLX    | LP3936SL        | 2500 units, Tape-and-Reel |

#### **Pin Description** Pin Name Description Type 1 GND\_BOOST Ground Power Switch Ground 2 FΒ Input Boost Converter Feedback 3 $V_{DD2}$ Power Supply Voltage for Internal Digital Circuits 4 GND2 Ground Ground Return for V<sub>DD2</sub> (Internal Digital) 5 WLED1 LED Output Open Drain, White LED1 Output WLED2 LED Output Open Drain, White LED2 Output 6 7 WLED3 LED Output Open Drain, White LED3 Output 8 WLED4 LED Output Open Drain, White LED4 Output 9 GND\_WLED Ground 4+2 White LED Driver Ground WLED5 Open Drain, White LED5 Output 10 LED Output 11 WLED6 LED Output Open Drain, White LED6 Output 12 Internal LDO Output, 2.8V $V_{DDA}$ Output 13 GND1 Ground Ground Return for V<sub>DD1</sub> (Internal Analog) 14 Power Supply Voltage for Internal Analog Circuits $V_{DD1}$ 15 AIN Input Ambient Light Sensor Input 16 **AREF** Output Reference Voltage for Ambient Light Sensor, 1.23V GND\_T 17 Ground 18 $V_{\mathsf{REF}}$ Output Internal Reference Bypass Capacitor 19 RT Input Oscillator Resistor 20 MW\_SEL MicroWire — I<sup>2</sup>C select (MW\_SEL=1 in MicroWire Mode) Logic Input **NRST** 21 Logic Input Low Active Reset Input CS MicroWire Chip-Select (in) / I2C SDA (in/out) 22 Logic Input/Output 23 DO Logic Output MicroWire Data Output 24 DΙ Logic Input MicroWire Data Input 25 SCL Logic Input MicroWire Clock / I<sup>2</sup>C SCL Input RGB\_EN 26 Logic Input LED Control for On/Off or PWM Dimming 27 Power Supply Voltage for Logic IO signals $V_{DD IO}$ 28 **ROUT** LED Output Open Drain Output, Red LED GOUT LED Output 29 Open Drain Output, Green LED

Open Drain Output, Blue LED

Open Drain, Boost Converter Power Switch

Ground for RGB Drivers

30

31

32

**BOUT**

GND\_RGB

OUT

LED Output

Ground

Output

#### Absolute Maximum Ratings (Notes 1,

2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{DD1},\ V_{DD2},\ V_{DD\_IO},\ V(OUT,\ FB)$  -0.3V to 6.0V Voltage on Logic Pins -0.3V to  $V_{DD\_IO}$  + 0.3V, with 6.0V max

Voltage on LED Output Pins -0.3V to V(FB) +

0.3V, with 6.0V max

Voltage on All Other Pins -0.3V to  $V_{DD1,2} +$

0.3V, with 6.0V max

I (ROUT, GOUT, BOUT) 150 mA I ( $V_{REF}$ ) 10  $\mu A$

Continuous Power Dissipation

(Note 3) Internally Limited

Junction Temperature (T<sub>J-MAX</sub>) 125°C

Storage Temperature Range -65°C to +150°C

Maximum Lead Temperature 260°C

(Reflow soldering, 3 times) (Note 4)

ESD Rating (Note 5)

Human Body Model: 2 kV Machine Model: 200V

### Operating Ratings (Notes 1, 2)

$\begin{array}{lll} V_{DD1}, \, V_{DD2} & 3.0 \text{V to } 6.0 \text{V} \\ V_{DD\_IO} & 1.65 \text{V} - V_{DD1,2} \\ \text{Recommended Load Current} & 0 \, \text{mA to } 250 \, \text{mA} \\ \text{Junction Temperature (T_J) Range} & -40^{\circ} \text{C to } +125^{\circ} \text{C} \end{array}$

Ambient Temperature (T<sub>A</sub>) Range

(Note 6)  $-40^{\circ}$ C to  $+85^{\circ}$ C

### **Thermal Properties**

Junction-to-Ambient Thermal Resistance  $(\theta_{JA})$ ,

SLD32A Package (Note 7) 72°C/W

#### Electrical Characteristics (Notes 2, 8)

Limits in standard typeface are for  $T_J$  = 25°C. Limits in **boldface** type apply over the operating ambient temperature range (-40°C  $\le T_A \le +85$ °C). Unless otherwise noted, specifications apply to the *Section Block Diagram* with:  $V_{DD1} = V_{DD2} = V_{DD_\_IO} = 3.6V$ ,  $C_{VDD1}$ ,  $C_{VDD2}$ ,  $C_{VDDIO} = 1$   $\mu$ F,  $C_{IN}$ ,  $C_{OUT} = 10$   $\mu$ F,  $C_{VDDA} = 1$   $\mu$ F,  $C_{VREF} = 0.1$   $\mu$ F,  $C_{BOOST} = 10$   $\mu$ H (Note 9).

| Symbol               | Parameter                                                  | Condition                        | Min   | Тур  | Max   | Units |

|----------------------|------------------------------------------------------------|----------------------------------|-------|------|-------|-------|

| $V_{\mathrm{DD1,2}}$ | Supply Voltage                                             |                                  | 3.0   | 3.6  | 6.0   | V     |

| I <sub>DD</sub>      | Standby Supply Current                                     | NSTBY = L (register)             |       | 1    | 7     | μA    |

|                      | (V <sub>DD1</sub> and V <sub>DD2</sub> current)            | CS, SCL, DI, NRST = H            |       |      |       |       |

|                      |                                                            | $V_{DD1}, V_{DD2} = 3.6V$        |       |      |       |       |

|                      | No-Load Supply Current                                     | NSTBY = H (reg.)                 |       | 170  | 300   | μΑ    |

|                      | (V <sub>DD1</sub> and V <sub>DD2</sub> current, boost off) | EN_BOOST = L (reg.)              |       |      |       |       |

|                      |                                                            | SCL, CS, DI, NRST = H            |       |      |       |       |

|                      | Full Load Supply Current                                   | NSTBY = H (register)             |       | 1    |       | mA    |

|                      | (V <sub>DD1</sub> and V <sub>DD2</sub> current, boost on)  | NRST, CS, SCL, DI = H            |       |      |       |       |

|                      |                                                            | RGB_EN = L                       |       |      |       |       |

|                      |                                                            | WLED1 6 = L                      |       |      |       |       |

|                      |                                                            | EN_AMBADC = L                    |       |      |       |       |

| I <sub>DD_IO</sub>   | V <sub>DD_IO</sub> Standby Supply Current                  | NSTBY = L (register)             |       | 1    |       | μΑ    |

|                      |                                                            | CS, SCL, DI, NRST = H            |       |      |       |       |

|                      | V <sub>DD IO</sub> Operating Supply Current                | 1 MHz Clock Frequency            |       | 20   |       | μA    |

|                      |                                                            | C <sub>L</sub> = 50 pF at DO pin |       |      |       |       |

| V <sub>REF</sub>     | Reference Voltage (Note 10)                                | I <sub>REF</sub> ≤ 1 nA,         | 1.205 | 1.23 | 1.255 | V     |

|                      |                                                            | Test Purposes Only               | -2    |      | +2    | %     |

| $V_{DDA}$            | LDO Output Voltage                                         | IV <sub>DDA</sub> < 1 μA         | 2.688 | 2.8  | 2.912 | % V   |

|                      |                                                            |                                  | -4    |      | +4    |       |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pins (GND1, GND2, GND\_T, GND\_BOOST, GND\_WLED, GND\_RGB).

Note 3: Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 160°C (typ.) and disengages at T<sub>J</sub> = 140°C (typ.).

Note 4: For detailed soldering specifications and information, please refer to National Semiconductor Application Note 1125: Laminate CSP/FBGA Package (AN-1125).

Note 5: The Human body model is a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin. MIL-STD-883 3015.7

### Electrical Characteristics (Notes 2, 8) (Continued)

Note 6: In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A-MAX})$  is dependent on the maximum operating junction temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power dissipation of the device in the application  $(P_{D-MAX})$ , and the junction-to ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 7: Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

Note 8: Min and Max limits are guaranteed by design, test, or statistical analysis. Typical numbers are not guaranteed, but do represent the most likely norm.

Note 9: Low-ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

Note 10: V<sub>REF</sub> pin (Bandgap reference output) is for internal use only. A capacitor should always be placed between V<sub>REF</sub> and GND1.

#### **Block Diagram**

### **Modes of Operation**

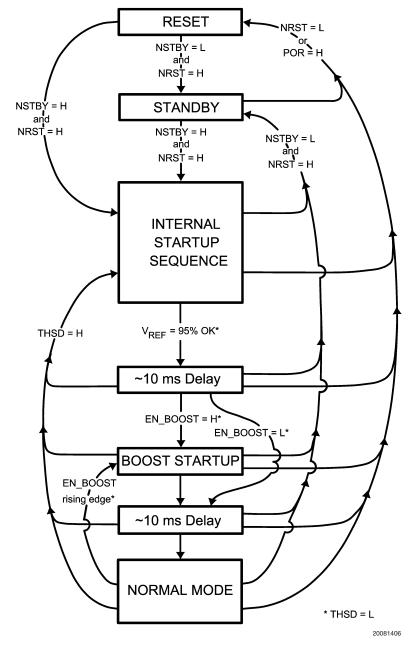

RESET: In the RESET mode all the internal registers are reset to the default values. Boost output register is set to

4.55V (register 0Dh = 07h), ext\_pwm is enabled for color outputs (register 2Bh = 1Ch), EN\_BOOST bit is high (register 0Bh bit 5) and all other registers are set to 00h. Reset is entered always if input NRST is LOW

or internal Power On Reset is active.

STANDBY: The STANDBY mode is entered if the register bit NSTBY is LOW and Reset is not active. This is the low

power consumption mode, when all circuit functions are disabled. Registers can be written in this mode and

the control bits are effective immediately after start up.

STARTUP: INTERNAL STARTUP SEQUENCE powers up all the needed internal blocks (V<sub>REF</sub>, Bias, Oscillator, etc.).

To ensure the correct oscillator initialization, a 10 ms delay is generated by the internal state-machine. Thermal shutdown (THSD) disables the chip operation and Startup mode is entered until *no* thermal

shutdown event is present.

BOOST STARTUP: Soft start for boost output is generated in the BOOST STARTUP mode. In this mode the boost output is

raised in PFM mode during the 10 ms delay generated by the state-machine. The Boost startup is entered from Internal Startup Sequence if EN\_BOOST is HIGH or from Normal mode when EN\_BOOST is written

HIGH. During Boost Startup all LEDs are turned off to reduce the loading.

NORMAL: During NORMAL mode the user controls the chip using the Control Registers. The registers can be written

in any sequence and any number of bits can be altered in a register in one write.

## Logic Interface Characteristics (1.8V $\leq$ V<sub>DD\_IO</sub> $\leq$ V<sub>DD1,2</sub>) (Note 11)

| Symbol           | Parameter              | Conditions                 | Min                      | Тур                      | Max | Units |

|------------------|------------------------|----------------------------|--------------------------|--------------------------|-----|-------|

| LOGIC INPU       | TS DI, SCL, NRST, RGB_ | EN, CS, MW_SEL             |                          |                          | •   |       |

| V <sub>IL</sub>  | Input Low Level        |                            |                          |                          | 0.5 | V     |

| V <sub>IH</sub>  | Input High Level       |                            | V <sub>DD_IO</sub> - 0.5 |                          |     | V     |

| I <sub>I</sub>   | Logic Input Current    |                            | -1.0                     |                          | 1.0 | μA    |

| f <sub>SCL</sub> | Clock Frequency        | I <sup>2</sup> C Mode      |                          |                          | 400 | kHz   |

|                  |                        | MicroWire Mode             |                          |                          | 8   | MHz   |

| LOGIC OUT        | PUTS DO, CS            |                            |                          |                          |     |       |

| V <sub>OL</sub>  | Output Low Level       | I <sub>DO, CS</sub> = 3 mA |                          | 0.3                      | 0.6 | V     |

| V <sub>OH</sub>  | Output High Level      | $I_{DO} = -3 \text{ mA}$   | V <sub>DD_IO</sub> - 0.6 | V <sub>DD_IO</sub> - 0.3 |     | V     |

| IL               | Output Leakage Current | $V_{DO} = 2.8V$            |                          |                          | 1.0 | μΑ    |

## Logic Interface Characteristics (1.65V $\leq$ V<sub>DD\_IO</sub> $\leq$ 1.8V) (Note 11)

| Symbol           | Parameter               | Conditions                | Min                       | Тур                      | Max  | Units |

|------------------|-------------------------|---------------------------|---------------------------|--------------------------|------|-------|

| LOGIC INPU       | JTS DI, SCL, NRST, RGB_ | EN, CS, MW_SEL            | •                         |                          |      |       |

| V <sub>IL</sub>  | Input Low Level         |                           |                           |                          | 0.35 | V     |

| V <sub>IH</sub>  | Input High Level        |                           | V <sub>DD_IO</sub> - 0.35 |                          |      | V     |

| I <sub>I</sub>   | Logic Input Current     |                           | -1.0                      |                          | 1.0  | μA    |

| f <sub>SCL</sub> | Clock Frequency         | I <sup>2</sup> C Mode     |                           |                          | 200  | kHz   |

|                  |                         | MicroWire Mode            |                           |                          | 4    | MHz   |

| LOGIC OUT        | PUTS DO, CS             |                           | •                         |                          |      |       |

| V <sub>OL</sub>  | Output Low Level        | I <sub>DO, CS</sub> = 2mA |                           | 0.3                      | 0.6  | V     |

| V <sub>OH</sub>  | Output High Level       | $I_{DO} = -2mA$           | V <sub>DD_IO</sub> - 0.6  | V <sub>DD_IO</sub> - 0.3 |      | V     |

| IL               | Output Leakage Current  | V <sub>DO</sub> = 2.8V    |                           |                          | 1.0  | μΑ    |

Note 11: In I $^2$ C mode operating ratings are limited to 3.0V  $\leq$  V<sub>DD1,2</sub>  $\leq$  4.5V and  $-20^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  +85 $^{\circ}$ C.

#### **Control Interface**

The LP3936 supports two different interfaces modes:

1) MicroWire/SPI interface

2) I<sup>2</sup>C compatible interface

User can define the interface by MW\_SEL pin. The pin configuration will also change depending on which interface  $\frac{1}{2}$

is selected. The following table shows the selections for both interface modes.

| MW_SEL | Interface                   | Pin Con  | figuration    | Comment                      |

|--------|-----------------------------|----------|---------------|------------------------------|

| 1      | MicroWire/SPI               | SCL      | (clock)       |                              |

|        |                             | DI       | (data in)     |                              |

|        |                             | DO       | (data out)    |                              |

|        |                             | CS       | (chip select) |                              |

| 0      | I <sup>2</sup> C Compatible | SCL      | (clock)       | Use pull up resistor for SCL |

|        |                             | CS = SDA | (data in/out) | Use pull up resistor for SDA |

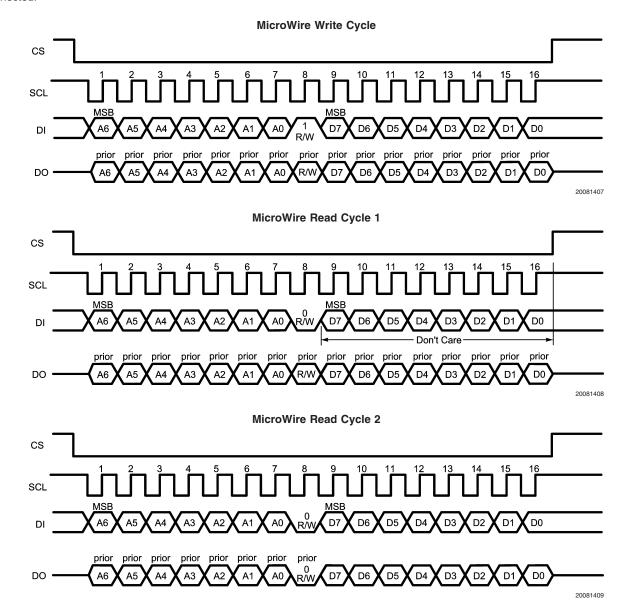

#### MicroWire/SPI Interface

The Microwire transmission consists of 16-bit Write and Read Cycles. One cycle consists of 7 Address bits, 1 Read/ Write (R/W) bit and 8 Data bits. Read is done in two cycles: address is provided in the first cycle and the data is sent out on the next cycle. R/W bit high state defines a Write Cycle and low defines a Read Cycle. DO output is normally in high-impedance state and it is active only during Write and Read Cycles. A pull-up or pull-down resistor may be needed in DO line if a floating logic signal can cause unintended current consumption in other circuits where DO is connected.

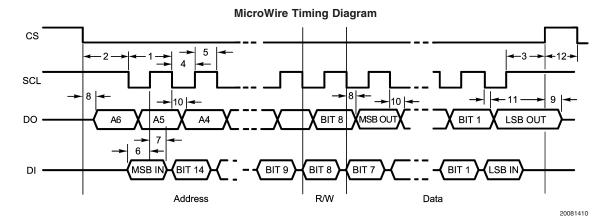

The Address and Data are transmitted MSB first. The Chip Select signal CS must be low during the Cycle transmission. CS resets the interface when high and it has to be taken high between successive Cycles. Data is clocked in on the rising edge of the SCL clock signal, while data is clocked out on the falling edge of SCL.

The MicroWire interface mode can also support SPI interface. The difference with normal SPI interface is that in LP3936 the Read operation from a new address needs two read cycles. If repetitive reads are made from the same address, a correct value is obtained on every read cycle.

#### MicroWire/SPI Interface (Continued)

### **MicroWire Timing Parameters**

$V_{DD1,2} = 3.0V - 6V, V_{DD\_IO} = 1.8V - V_{DD1,2}$

| Cumbal | Parameter             | Limit |     | Units |

|--------|-----------------------|-------|-----|-------|

| Symbol | Parameter             | Min   | Max | Units |

| 1      | Cycle Time            | 120   |     | ns    |

| 2      | Enable Lead Time      | 60    |     | ns    |

| 3      | Enable Lag Time       | 60    |     | ns    |

| 4      | Clock Low Time        | 60    |     | ns    |

| 5      | Clock High Time       | 60    |     | ns    |

| 6      | Data Setup Time       | 0     |     | ns    |

| 7      | Data Hold Time        | 10    |     | ns    |

| 8      | Data Access Time      |       | 35  | ns    |

| 9      | Disable Time          |       | 30  | ns    |

| 10     | Output Data Valid     |       | 55  | ns    |

| 11     | Output Data Hold Time | 15    |     | ns    |

| 12     | CS Inactive Time      | 10    |     | ns    |

Note: Data guaranteed by design.

## I<sup>2</sup>C Compatible Interface

#### I<sup>2</sup>C SIGNALS

In I<sup>2</sup>C mode the LP3936 pin SCL is used for the I<sup>2</sup>C clock and the pin CS is used for the I<sup>2</sup>C data signal SDA. Both these signals need a pull-up resistor according to I<sup>2</sup>C specification. Unused pin DO can be left unconnected and pin DI must be connected to  $V_{DD\_IO}$  or GND.

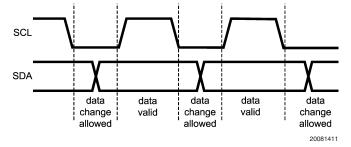

#### I<sup>2</sup>C DATA VALIDITY

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when CLK is LOW.

.

### I<sup>2</sup>C Compatible Interface (Continued)

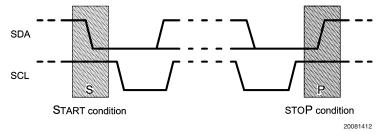

#### I<sup>2</sup>C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of the I<sup>2</sup>C session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP bits. The I<sup>2</sup>C bus is considered to be busy after START condition and free after STOP condition. During data transmission, I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

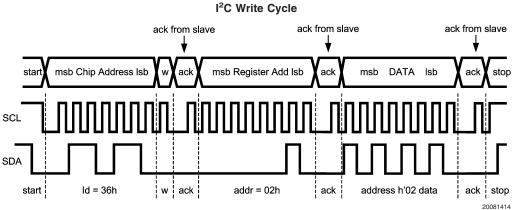

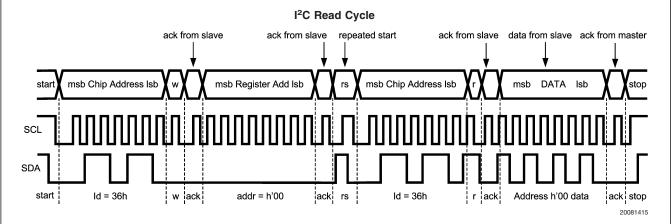

#### TRANSFERRING DATA

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the 9th clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

After the START condition, the  $I^2C$  master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LP3936 address is 36h. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

#### I<sup>2</sup>C Chip Address MSB **LSB** ADR5 ADR6 ADR4 ADR3 ADR2 ADR1 ADR0 R/W bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0 0 0 0 I<sup>2</sup>C SLAVE address (chip address)

20081413

w = write (SDA = "0") r = read (SDA = "1")

ack = acknowledge (SDA pulled down by either master or slave)

rs = repeated start

id = chip address, 36h for LP3936

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in the Read Cycle waveform.

## I<sup>2</sup>C Compatible Interface (Continued)

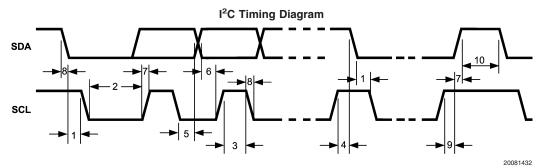

## I<sup>2</sup>C Timing Parameters

$V_{\rm DD1,\ 2}$  = 3.0V to 4.5V,  $V_{\rm DD\_IO}$  = 1.65V to  $V_{\rm DD1,\ 2}$

| Compleal       | Parameter                                                    | Lin                    | nits | Units |

|----------------|--------------------------------------------------------------|------------------------|------|-------|

| Symbol         | Parameter                                                    | Min                    | Max  | Units |

| 1              | Hold Time (repeated) START Condition                         | 0.6                    |      | μs    |

| 2              | Clock Low Time                                               | 1.3                    |      | μs    |

| 3              | Clock High Time                                              | 600                    |      | ns    |

| 4              | Setup Time for a Repeated START Condition                    | 600                    |      | ns    |

| 5              | Data Hold Time (output direction, delay generated by LP3936) | 300                    | 900  | ns    |

| 5              | Data Hold Time (input direction)                             | 0                      | 900  | ns    |

| 6              | Data Setup Time                                              | 100                    |      | ns    |

| 7              | Rise Time of SDA and SCL                                     | 20 + 0.1C <sub>b</sub> | 300  | ns    |

| 8              | Fall Time of SDA and SCL                                     | 15 + 0.1C <sub>b</sub> | 300  | ns    |

| 9              | Set-Up Time for STOP Condition                               | 600                    |      | ns    |

| 10             | Bus Free Time between a STOP and a START Condition           | 1.3                    |      | μs    |

| C <sub>b</sub> | Capacitive Load for Each Bus Line                            | 10                     | 200  | pF    |

Note: Data guaranteed by design.

### A/D Converter for Ambient Light Measurement Electrical Characteristics

| Symbol                | Parameter                  | Conditions                 | Min  | Тур  | Max  | Units |

|-----------------------|----------------------------|----------------------------|------|------|------|-------|

| V <sub>IN RANGE</sub> | Input Voltage              | AD Output: 00h             |      | 1.23 |      | V     |

|                       |                            | AD Output: FFh             |      | 2.46 |      | V     |

| DNL                   | Differential Non-Linearity |                            | -1.5 | ±1   | +1.5 | LSB   |

| GE                    | Gain Error                 |                            | -5   |      | +5   | LSB   |

| PSS                   | Power Supply Sensitivity   | $3.1V \le V_{DD} \le 4.2V$ |      | ±1/2 |      | LSB   |

| f(conv)               | Conversion Rate            | Without Averaging          |      | 217  |      | Hz    |

|                       |                            | With Averaging             |      | 3.4  |      | Hz    |

|                       |                            | (64 samples)               |      | 3.4  |      | П     |

| t <sub>STARTUP</sub>  | Startup Time               |                            |      | 100  |      | ms    |

| I <sub>AIN</sub>      | Input Current              | 1.23 < AIN < 2.6V          |      | ±0.1 |      | μΑ    |

| I <sub>AREF</sub>     | Maximum Output Current     | AREF Output Current Sink   |      | 200  |      | μΑ    |

| R <sub>AREF</sub>     | AREF Output Resistance     |                            |      | 110  |      | Ω     |

ADC output AIN[7:0] can be read from address 0CH after startup time. Overflow bit can be read from bit D7 in address 0BH. The overflow bit indicates that input voltage exceeds the input voltage range of the ADC. The ADC output value in this case is FFH. When averaging is on, the overflow is high, if any of the 64 conversion results in the averaging period overflows. Thus the averaged result may be considerably below maximum and the overflow can still be high, if the input signal is noisy.

Examples for optical sensor are photodiode SHF2400 and phototransistor SFH3410 from Osram or BSC 3216 G1 optical sensor from TDK.

ADC can be used for temperature measurement with a thermistor. It enables temperature compensated LED driving. If ADC is not used, it should be disabled by writing en\_ambadc bit low. AIN and AREF pins can be left unconnected

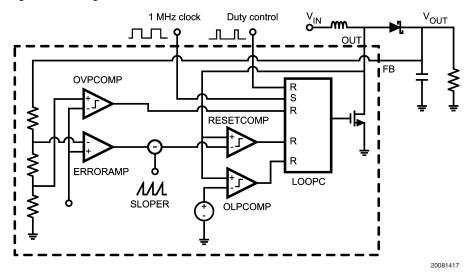

### **Magnetic Boost DC/DC Converter**

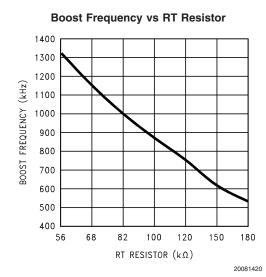

The LP3936 Boost DC/DC Converter generates a 4.1V-5.3V supply voltage for the LEDs from single Li-lon battery (3V ... 4.5V). The output voltage is controlled with an 8-bit register in 9 steps. The converter is a magnetic switching PFM/PWM mode DC/DC converter with a current limit. The converter has a 1 MHz switching frequency when timing resistor RT is 82 k $\Omega$ .

The topology of the magnetic boost converter is called CPM control, current programmed mode, where the inductor current is measured and controlled with the feedback. The user can program the output voltage of the boost converter. The control changes the resistor divider in the feedback loop.

The following figure shows the boost topology with the protection circuitry. Three different protection schemes are implemented:

- 1) Over voltage protection, limits the maximum output voltage

- a. Keeps the output below breakdown voltage.

- b. Prevents boost operation if battery voltage is much higher than desired output.

- 2) Over current protection, limits the maximum inductor current

- a. Voltage over switching NMOS is monitored; too high voltages turn the switch off.

- 3) Duty cycle limiting, done with digital control.

### **Boost Output Voltage Control**

User can control the boost output voltage by boost output 8-bit register.

| Boost[7:0]<br>Register 0Dh |     | BOOST Output<br>Voltage |

|----------------------------|-----|-------------------------|

| Binary                     | Hex | (typical)               |

| 0000 0000                  | 00  | 4.10                    |

| 0000 0001                  | 01  | 4.25                    |

| 0000 0011                  | 03  | 4.40                    |

| 0000 0111                  | 07  | 4.55 Default            |

| 0000 1111                  | 0F  | 4.70                    |

| 0001 1111                  | 1F  | 4.85                    |

| 0011 1111                  | 3F  | 5.00                    |

| 0111 1111                  | 7F  | 5.15                    |

| 1111 1111                  | FF  | 5.30                    |

TIME (200 µs/DIV)

20081418

### Magnetic Boost DC/DC Converter Electrical Characteristics

| Symbol               | Parameter                        | Conditions                                                                                                         | Min | Тур                                      | Max  | Units |

|----------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------|------|-------|

| I <sub>LOAD</sub>    | Load Current                     | $3.0V \le V_{IN} \le 4.5V$<br>$V_{OUT} = 4.55V$                                                                    | 0   |                                          | 250  | mA    |

| V <sub>OUT</sub>     | Output Voltage Accuracy (FB Pin) | $1 \text{ mA} \le I_{LOAD} \le 225 \text{ mA}$<br>$3.0V \le V_{IN} \le V \text{ (FB)} - 0.5V$<br>$V_{OUT} = 4.55V$ | -5  |                                          | +5   | %     |

|                      | Output Voltage (FB Pin)          | 1 mA $\leq$ I <sub>LOAD</sub> $\leq$ 250 mA<br>3.0V $<$ V <sub>IN</sub> $<$ 4.55V +<br>V <sub>(SCHOTTKY)</sub>     |     | 4.55                                     |      | V     |

|                      |                                  |                                                                                                                    |     | V <sub>IN</sub> -V <sub>(SCHOTTKY)</sub> |      | V     |

| RDS <sub>ON</sub>    | Switch ON Resistance             | $V_{DD1,2} = 3.6V, I_{SW} = 0.5A$                                                                                  |     | 0.4                                      | 0.5  | Ω     |

| f <sub>PWF</sub>     | PWM Mode Switching Frequency     | RT = 82 kΩ                                                                                                         |     | 1                                        |      | MHz   |

|                      | Frequency Accuracy               | RT = 82 kΩ                                                                                                         | -6  | ±3                                       | +6   | %     |

|                      |                                  |                                                                                                                    | -10 |                                          | +10  | %     |

| t <sub>STARTUP</sub> | Startup Time                     |                                                                                                                    |     | 25                                       |      | ms    |

| I <sub>CL_OUT</sub>  | OUT Pin Current Limit            | V <sub>DD</sub> = 3.6V                                                                                             | 600 | 750                                      | 1050 | mA    |

|                      |                                  |                                                                                                                    | 400 |                                          | 1200 | IIIA  |

#### PFM/PWM Mode

User can change the Boost converters mode between PWM (Pulse Width Modulation) and PFM (Pulse Frequency Modulation). The startup is done on PFM mode and then the device runs on PWM mode (as a default). User can set PFM mode by turning "pfm\_mode" register bit HIGH. PFM is recommended to use with light loads and PWM with high loads.

### **Boost Standby Mode**

User can set boost converter to STANDBY mode by writing register bit EN\_BOOST low. This mode can be useful when driving LEDs directly from battery voltage. This may be possible if LED forward voltage is low, battery voltage is high and LED current is low.

When EN\_BOOST is written high, the converter starts for 10 ms in PFM mode and then goes to PWM mode if PWM mode has been selected (default). During Boost Start-up all LEDs are turned off to reduce the load.

#### **Unused Boost Converter**

If the boost converter is not used, it should be disabled by writing bit en\_boost low. OUT pin should be connected to GND and FB pin to the LED supply voltage.

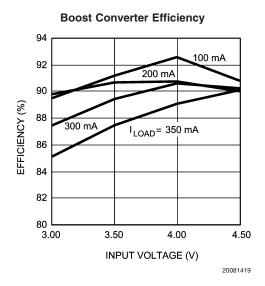

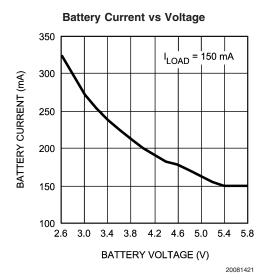

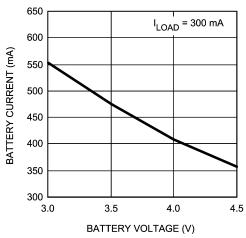

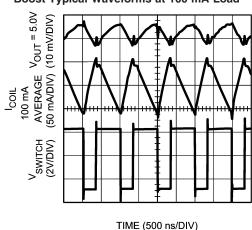

## **Boost Converter Typical Performance Characteristics** $V_{IN} = 3.6V$ , $V_{OUT} = 4.55V$ if not otherwise stated.

## Boost Converter Typical Performance Characteristics $V_{\text{IN}}$ = 3.6V, $V_{\text{OUT}}$ = 4.55V if not

otherwise stated. (Continued)

#### **Battery Current vs Voltage**

20081422

#### Boost Typical Waveforms at 100 mA Load

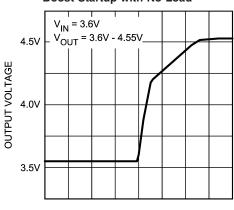

**Boost Startup with No Load**

TIME (50 µs/DIV)

20081424

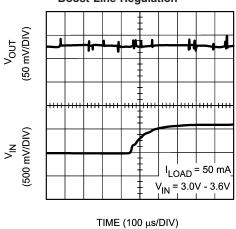

### **Boost Line Regulation**

20081423

20081425

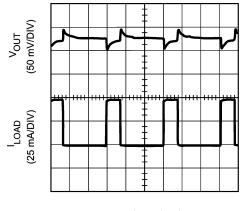

Boost Load Regulation, 50 mA-100 mA

TIME (50 µs/DIV)

20081426

15

#### **RGB LED Driver**

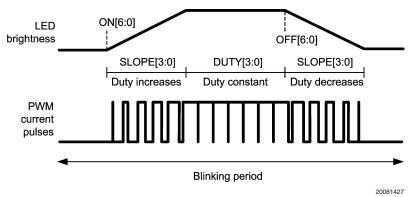

The RGB driver has three outputs that can independently drive one RGB LED or three LEDs of any kind. User has control over the following parameters separately for each LED:

• ON and OFF (start and stop time in blinking cycle)

• **DUTY** (PWM brightness control)

• SLOPE (dimming slope)

• ENABLE (direct enable control)

The main blinking cycle is controlled with 2-bit CYCLE control (0.25 / 0.5 / 1.0 / 2.0s).

**RGB PWM Operating Principle**

RGB\_START is the master enable control for the whole RGB function. The internal PWM and blinking control can be disabled by setting the RGB\_PWM control LOW. In this case the individual enable controls can be used to switch outputs on and off. RGB\_EN input can be used for external hardware PWM control. RGB\_EN input can be used as direct on/off or brightness (PWM) control. If RGB\_EN input is not used, it must be tied to  $V_{\rm DD\_IO}$ . Recommended maximum frequency of RGB LED external PWM control is 1 MHz.

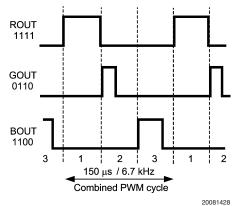

In the normal PWM mode the R, G and B switches are controlled in 3 phases (one phase per driver). During each phase the peak current set by external resistor is driven through the LED for the time defined by DUTY setting (0  $\mu s$ –50  $\mu s$ ). As a time averaged current this means 0%–33% of the peak current. The PWM period is 150  $\mu s$  and the pulse frequency is 6.67 kHz in normal mode.

Normal Mode PWM Waveforms at different duty settings

In the FLASH mode all the outputs are controlled in one phase and the PWM period is 50  $\mu$ s. The time averaged FLASH mode current is three times the normal mode current at the same DUTY value.

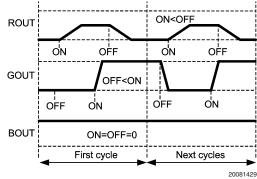

Blinking can be controlled separately for each output. On and OFF times determine, when a LED turns on and off within the blinking cycle. When both ON and OFF are 0, the LED is on and doesn't blink. If ON equals OFF but is not 0, the LED is permanently off.

**Example Blinking Waveforms**

### **RGB Driver Electrical Characteristics**

$(\mathsf{R}_\mathsf{OUT},\,\mathsf{G}_\mathsf{OUT},\,\mathsf{B}_\mathsf{OUT}\;\mathsf{outputs})$

| Symbol                  | Parameter                 | Conditions             | Min | Тур  | Max | Units |

|-------------------------|---------------------------|------------------------|-----|------|-----|-------|

| R <sub>DS-ON</sub>      | ON Resistance             |                        |     | 2    | 4.5 | Ω     |

| I <sub>LEAKAGE</sub>    | Off State Leakage Current | V <sub>FB</sub> = 5.3V |     | 0.04 | 1   | μA    |

| I <sub>MAX</sub>        | Maximum Sink Current      | (Note 12)              |     |      | 120 | mA    |

| T <sub>SMAX</sub>       | Maximum Slope Period      | Maximum Duty Setting   |     | 0.93 |     | S     |

| T <sub>SMIN</sub>       | Minimum Slope Period      | Maximum Duty Setting   |     | 31   |     | ms    |

| T <sub>SRES</sub>       | Slope Resolution          | Maximum Duty Setting   |     | 62   |     | ms    |

| T <sub>START/STOP</sub> | Start/Stop Resolution     | Cycle 1s               |     | 1/16 |     | S     |

| Duty                    | Duty Step Size            |                        |     | 1/16 |     |       |

| T <sub>BLINK</sub>      | Blinking Cycle Accuracy   |                        | -6  | ±3   | +6  | %     |

| D <sub>CYCF</sub>       | Duty Cycle Range          | EN_FLASH = 1           | 0   |      | 94  | %     |

| D <sub>CYC</sub>        | Duty Cycle Range          | EN_FLASH = 0           | 0   |      | 31  | %     |

| D <sub>RESF</sub>       | Duty Resolution           | EN_FLASH = 1 (4-bit)   |     | 6.27 |     | %     |

| D <sub>RES</sub>        | Duty Resolution           | EN_FLASH = 0 (4-bit)   |     | 2.09 |     | %     |

| F <sub>PWMF</sub>       | PWM Frequency             | EN_FLASH = 1           |     | 20   |     | kHz   |

| F <sub>PWM</sub>        | PWM Frequency             | EN_FLASH = 0           |     | 6.67 |     | kHz   |

Note 12: The total load current of the boost converter should be limited to 250 mA.

### RGB LED PWM Control (Note 13)

| _                        |                                                                                                                                                                                                             |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDUTY[3:0]<br>GDUTY[3:0] | DUTY sets the brightness of the LED by adjusting the duty cycle of the PWM driver. The minimum DUTY cycle [0000] is 0% and the maximum [1111] in the Flash mode is $\sim$ 94% and in the normal mode 31% of |

| BDUTY[3:0]               | the peak pulse current. The peak pulse current is determined by the external resistor, LED forward voltage drop and the boost voltage.                                                                      |

| RSLOPE[3:0]              | SLOPE sets the turn-on and turn-off slopes. Fastest slope is set by [0000] and slowest by [1111]. SLOPE                                                                                                     |

| GSLOPE[3:0]              | changes the duty cycle at constant, programmable rate. For each slope setting the maximum slope time                                                                                                        |

| BSLOPE[3:0]              | appears at maximum DUTY setting. When DUTY is reduced, the slope time decreases proportionally. For example, in case of maximum DUTY, the sloping time can be adjusted from 31 ms [0000] to 930 ms          |

|                          | [1111]. For 50% DUTY [1000] the sloping time is 17 ms [0000] to 496 ms [1111]. The blinking cycle has <b>no</b> effect on SLOPE.                                                                            |

| RON[6:0]                 | ON sets the beginning time of the turn-on slope. The on-time is relative to the selected blinking cycle                                                                                                     |

| GON[6:0]                 | length. On-setting N (N = 0–127) sets the on-time to N/128 $^{\star}$ cycle length.                                                                                                                         |

| BON[6:0]                 |                                                                                                                                                                                                             |

| ROFF[6:0]                | OFF sets the beginning time of the turn-off slope. Off-time is relative to blinking cycle length in the same                                                                                                |

| GOFF[6:0]                | way as on-time.                                                                                                                                                                                             |

| BOFF[6:0]                |                                                                                                                                                                                                             |

|                          | If ON = 0, OFF = 0 and RGB_PWM = 1, then RGB outputs are continuously on (no blinking), DUTY                                                                                                                |

|                          | controls the brightness and SLOPE is ignored.                                                                                                                                                               |

|                          | If ON and OFF are the same, but not 0, RGB outputs are turned off.                                                                                                                                          |

| CYCLE[1:0]               | CYCLE sets the blinking cycle: [00] for 0.25s, [01] for 0.5s, [10] for 1s and [11] for 2s. CYCLE setting is common to all R, G and B drivers.                                                               |

| RSW                      | Enable for R switch                                                                                                                                                                                         |

| GSW                      | Enable for G switch                                                                                                                                                                                         |

| BSW                      | Enable for B switch                                                                                                                                                                                         |

| RGB_START                | Master Switch:                                                                                                                                                                                              |

|                          | $RGB\_START = 0 \rightarrow RGB OFF$                                                                                                                                                                        |

|                          | RGB_START = 1 $\rightarrow$ RGB ON, starts the new cycle from t = 0                                                                                                                                         |

| RGB_PWM                  | RGB_PWM = 0 → RSW, GWS and BSW control directly the RGB outputs (on/off control only)                                                                                                                       |

|                          | RGB_PWM = 1 → Normal PWM RGB functionality (duty, slope, on/off times, cycle)                                                                                                                               |

| EN_FLASH                 | Flash Mode enable control for RGB. In Flash mode (EN_FLASH = 1) RGB outputs are PWM controlled                                                                                                              |

|                          | simultaneously, not in 3-phase system as in the Normal Mode.                                                                                                                                                |

### RGB LED PWM Control (Note 13) (Continued)

| EN_RED_PWM   | $EN_X_PWM = 0 \rightarrow External PWM control from RGB_EN pin is disabled$ |

|--------------|-----------------------------------------------------------------------------|

| EN_GREEN_PWM | $EN_X_PWM = 1 \rightarrow External PWM control from RGB_EN pin is enabled$  |

| EN BLUE PWM  | Internal PWM control (DUTY) can be used independently of external PWM       |

Internal PWM control (DUTY) can be used independently of external PWM control. External PWM has the same effect on all enabled colors.

Note 13: Application Note AN-1293, "Driving RGB LEDs Using LP3936 Lighting Management System" contains a thorough description of the RGB driver functionality including programming examples.

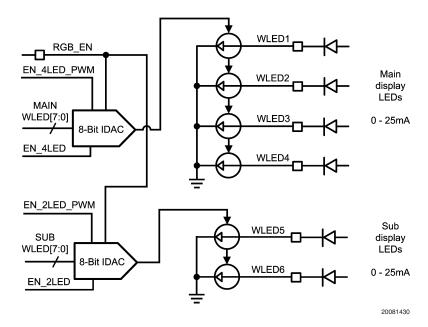

#### **WLED Drivers**

White LED drivers drive each white LED with a regulated constant current. The outputs are combined in two groups, four outputs for the main display backlight and two outputs for the sub display backlight. The current is controlled between 0 and 25.5 mA using the 8-bit current mode DA-converters. WLED outputs can be used to drive any kind of LED.

Main and sub display outputs have separate enable control bits, EN\_4LED and EN\_2LED.

PWM control of WLED outputs for dimming or on/off control is possible using RGB\_EN pin together with EN\_4LED\_PWM and EN\_2LED\_PWM enable control bits from the user register. Recommended maximum frequency of WLED external PWM control is 1 kHz.

#### WLED and CLED Driver Electrical Characteristics

| Symbol Parameter     |                                 | Conditions                                               | Min | Тур    | Max | Units |

|----------------------|---------------------------------|----------------------------------------------------------|-----|--------|-----|-------|

| I <sub>RANGE</sub>   | Sink Current Range              | V <sub>FB</sub> = 4.55V, Control 00h–FFh                 |     | 0-25.5 |     | mA    |

| I <sub>MAX</sub>     | Maximum Sink Current            | (Note 14)                                                | 24  | 25.5   | 27  | mA    |

|                      |                                 |                                                          | 22  |        | 28  | mA    |

| I <sub>LEAKAGE</sub> | Leakage Current                 | V <sub>FB</sub> = 5V                                     |     | 0.04   | 1   | μA    |

| I <sub>MATCH</sub>   | Sink Current Matching (Note 15) | I <sub>SINK</sub> = 13 mA, between<br>WLED1 4 or WLED5 6 |     | 1.0    | 4   | %     |

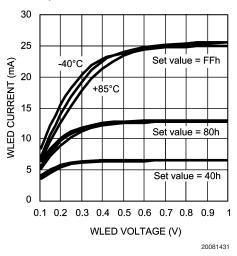

Note 14: A minimum voltage, Dropout Voltage, is required on the WLED outputs for maintaining the LED current. The current reduction at lower voltages is shown in the graph WLED Output Current vs. Voltage.

Note 15: Match % = 100% \* (Max - Min)/Min

#### **WLED Current Adjustment**

| WLED[7:0] | WLED Current<br>(Typical) | Units |

|-----------|---------------------------|-------|

| 0000 0000 | 0                         | mA    |

| 0000 0001 | 0.1                       | mA    |

| 0000 0010 | 0.2                       | mA    |

| 0000 0011 | 0.3                       | mA    |

| •         | •                         | •     |

| •         | •                         | •     |

| 1111 1101 | 25.3                      | mA    |

| 1111 1110 | 25.4                      | mA    |

| 1111 1111 | 25.5                      | mA    |

#### WLED Output Current vs Voltage Temperatures -40°C, +25°C, +85°C

# Recommended External Components

#### **OUTPUT CAPACITOR, COUT**

The output capacitor  $C_{\text{OUT}}$  directly affects the magnitude of the output ripple voltage. In general, the higher the value of  $C_{\text{OUT}}$ , the lower the output ripple magnitude. Multilayer ceramic capacitors with low ESR are the best choice. At the

lighter loads, the low ESR ceramics offer a much lower  $V_{\rm OUT}$  ripple than the higher ESR tantalums of the same value. At the higher loads, the ceramics offer a slightly lower  $V_{\rm OUT}$  ripple magnitude than the tantalums of the same value. However, the dv/dt of the  $V_{\rm OUT}$  ripple with the ceramics is much lower than the tantalums under all load conditions. Capacitor voltage rating must be sufficient, 10V is recommended. It should be noted that with some capacitor types the actual capacitance depends heavily on the capacitor DC voltage bias.

#### INPUT CAPACITOR, CIN

The input capacitor  $C_{\text{IN}}$  directly affects the magnitude of the input ripple voltage and to a lesser degree the  $V_{\text{OUT}}$  ripple. A higher value  $C_{\text{IN}}$  will give a lower  $V_{\text{IN}}$  ripple. Capacitor voltage rating must be sufficient, 10V is recommended.

#### OUTPUT DIODE, $D_{OUT}$

A Schottky diode should be used for the output diode. To maintain high efficiency the average current rating of the schottky diode should be larger than the peak inductor current (1A). Schottky diodes with a low forward drop and fast switching speeds are ideal for increasing efficiency in portable applications. Choose a reverse breakdown of the schottky diode larger than the output voltage. Do not use ordinary rectifier diodes, since slow switching speeds and long recovery times cause the efficiency and the load regulation to suffer.

#### INDUCTOR, L

The high switching frequency enables the use of the small surface mount inductor. A 10 µH shielded inductor is suggested. Values below 4.7 µH should not be used. The inductor should have a saturation current rating higher than the peak current it will experience during circuit operation ( $\sim$ 1A). Less than 300 m $\Omega$  ESR is suggested for high efficiency. Open core inductors cause flux linkage with circuit components and interfere with the normal operation of the circuit. This should be avoided. For high efficiency, choose an inductor with a high frequency core material such as ferrite to reduce the core losses. To minimize radiated noise, use a toroid, pot core or shielded core inductor. The inductor should be connected to the OUT pin as close to the IC as possible. Examples of suitable inductors are TDK types LLF4017T-100MR90C and VLF4012AT-100MR79 and Coilcraft type DO3314T-103 (unshielded).

#### List of Recommended External Components

| Symbol             | Symbol Explanation                                              | Value | Unit | Туре                                          |

|--------------------|-----------------------------------------------------------------|-------|------|-----------------------------------------------|

| C <sub>VDD1</sub>  | V <sub>DD1</sub> bypass capacitor                               | 1     | μF   | Ceramic, X7R                                  |

| C <sub>VDD2</sub>  | V <sub>DD2</sub> bypass capacitor                               | 1     | μF   | Ceramic, X7R                                  |

| C <sub>OUT</sub>   | Output capacitor from FB to GND                                 | 10    | μF   | Ceramic, X7R/Y5V                              |

| C <sub>IN</sub>    | Input capacitor from Battery Voltage to GND                     | 10    | μF   | Ceramic, X7R/Y5V                              |

| C <sub>VDDIO</sub> | V <sub>DDIO</sub> bypass capacitor                              | 1     | μF   | Ceramic, X7R                                  |

| C <sub>VDDA</sub>  | Internal LDO output capacitor, between V <sub>DDA</sub> and GND | 1     | μF   | Ceramic, X7R                                  |

| RT                 | Oscillator Frequency Bias Resistor                              | 82    | kΩ   | 1% (Note 16)                                  |

| RDO                | DO output pull-up resistor                                      | 100   | kΩ   |                                               |

| C <sub>VREF</sub>  | Reference Voltage Capacitor, between V <sub>REF</sub> and GND   | 100   | nF   | Ceramic, X7R                                  |

| L <sub>BOOST</sub> | Boost converter inductor                                        | 10    | μH   | Shielded, Low ESR, I <sub>SAT</sub> $\sim$ 1A |

| D <sub>OUT</sub>   | Rectifying Diode, V <sub>F</sub> @ Maxload                      | 0.3   | V    | Schottky Diode                                |

### Recommended External Components (Continued)

List of Recommended External Components (Continued)

| Symbol                            | Symbol Explanation      | Value                                                        | Unit      | Туре         |  |  |

|-----------------------------------|-------------------------|--------------------------------------------------------------|-----------|--------------|--|--|

| RGB                               | RGB LED                 | User Defined (See Application Note AN-1293 for resistor size |           |              |  |  |

| R <sub>R</sub> , R <sub>G</sub> , | Current Limit Resistors |                                                              |           |              |  |  |

| R <sub>B</sub>                    |                         | (366 /                                                       | тррпсацоп | calculation) |  |  |

| LEDs                              | White LEDs              | - Galdulation)                                               |           |              |  |  |

Note 16: Resistor RT tolerance change will change the timing accuracy of the RGB block. Also the boost converter switching frequency will be affected.

### **Control Registers**

All user accessible control registers and register bits are shown in the following table.

| ADDR | SETUP            | D7        | D6        | D5        | D4        | D3          | D2         | D1         | D0         |

|------|------------------|-----------|-----------|-----------|-----------|-------------|------------|------------|------------|

| 00H  | Control register | rgb_pwm   | rgb_start | cycle[1]  | cycle[0]  | rsw         | gsw        | bsw        | pfm_mode   |

| 01H  | ron              |           | ron[6]    | ron[5]    | ron[4]    | ron[3]      | ron[2]     | ron[1]     | ron[0]     |

| 02H  | roff             |           | roff[6]   | roff[5]   | roff[4]   | roff[3]     | roff[2]    | roff[1]    | roff[0]    |

| 03H  | gon              |           | gon[6]    | gon[5]    | gon[4]    | gon[3]      | gon[2]     | gon[1]     | gon[0]     |

| 04H  | goff             |           | goff[6]   | goff[5]   | goff[4]   | goff[3]     | goff[2]    | goff[1]    | goff[0]    |

| 05H  | bon              |           | bon[6]    | bon[5]    | bon[4]    | bon[3]      | bon[2]     | bon[1]     | bon[0]     |

| 06H  | boff             |           | boff[6]   | boff[5]   | boff[4]   | boff[3]     | boff[2]    | boff[1]    | boff[0]    |

| 07H  | rslope, rduty    | rslope[3] | rslope[2] | rslope[1] | rslope[0] | rduty[3]    | rduty[2]   | rduty[1]   | rduty[0]   |

| 08H  | gslope, gduty    | gslope[3] | gslope[2] | gslope[1] | gslope[0] | gduty[3]    | gduty[2]   | gduty[1]   | gduty[0]   |

| 09H  | bslope, bduty    | bslope[3] | bslope[2] | bslope[1] | bslope[0] | bduty[3]    | bduty[2]   | bduty[1]   | bduty[0]]  |

| 0AH  | wled current 1   | wled1[7]  | wled1[6]  | wled1[5]  | wled1[4]  | wled1[3]    | wled1[2]   | wled1[1]   | wled1[0]   |

| 0BH  | enables          | overflow  | nstby     | en_boost  | en_flash  | en_ambave   | en_ambadc  | en_4led    | en_2led    |

| 0CH  | Amb. Light data  | ain[7]    | ain[6]    | ain[5]    | ain[4]    | ain[3]      | ain[2]     | ain[1]     | ain[0]     |

| 0DH  | boost output     | boost[7]  | boost[6]  | boost[5]  | boost[4]  | boost[3]    | boost[2]   | boost[1]   | boost[0]   |

| 2AH  | wled current 2   | wled2[7]  | wled2[6]  | wled2[5]  | wled2[4]  | wled2[3]    | wled2[2]   | wled2[1]   | wled2[0]   |

| 2BH  | ext pwm enable   |           |           |           | en_redpwm | en_greenpwm | en_bluepwm | en_4ledpwm | en_2ledpwm |

Default value of each register is 0000 0000 except the following

- boost output default is 0000 0111 = 07h (4.55V).

- enables default is x010 0000 = 20h (boost enabled)

- ext\_pwm\_enable default is 0001 1100 = 1Ch (RGB\_EN control enabled for color outputs)

Register 0Ch all bits (ain[7:0]) and bit D7 in register 0Bh (overflow) are read only. All other bits are read-write.

#### Physical Dimensions inches (millimeters) unless otherwise noted

DIMENSIONS ARE IN MILLIMETERS

RECOMMENDED LAND PATTERN

1:1 RATIO WITH PACKAGE SOLDER PADS

SLD32A (Rev A)

32-Lead Thin CSP Package, 4.5 x 5.5 x 0.8 mm, 0.5 mm Pitch NS Package Number SLD32A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560